关于石英晶振相关的电路设计考虑

电线板的设计主要是由电气设备和电子元器件按一定方式联接起来,为电流流通提供了路径的总体,也叫电子网路。电路的大小可以相差很大,小到硅片上的集成电路,大到输电网。电路或称电子回路,是由电气设备和元器件,按一定方式联接起来,为电荷流通提供了路径的总体,也叫电子线路或称电气回路,简称网络或回路。如32.768K、电阻、电容、电感、二极管、三极管和开关等,构成的网络。很很多的工程在设计电路板的时候都会遇到一些问题,该篇文章给大家的讲解关于设计时候的一些考虑.

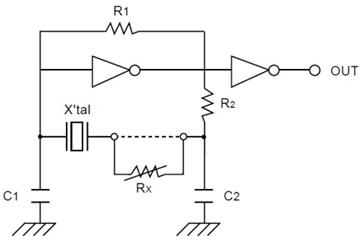

设计考虑:为了石英晶体振荡器电路的良好运行,某些设计应遵循考虑因素。在所有情况下,建议在中避免平行轨迹以便减小电路杂散电容。所有迹线应尽可能短,组件应尽可能短,应该隔离以防止耦合。接地层应该用来隔离信号。

负电阻:为了获得最佳性能,必须在中设计振荡器电路,这种增强“负电阻”的方式,有时被称为“振荡裕量”。对给定电路中负电阻量的评估是通过临时安装与石英晶振单元串联的可变电阻器。电阻器应该被初始设置在其最低设置,优选接近零欧姆。振荡器被启动,输出被监控示波器。然后调整可变电阻器,使得输出被持续监测。

在某个电阻值时,振荡将停止。此时,该测量可变电阻以确定振荡停止时的欧姆值。为此值,将必须增加供应商规定的贴片晶振单元的最大电阻。总欧姆电阻被认为是“负电阻”或“振荡裕量”。永远可靠电路运行时,建议负电阻至少为

晶体单元的规定最大电阻值。

超过晶体单元最大电阻五倍的负电阻值为更好。由于负电阻在高温下趋于降低,因此建议测试在工作范围的最高温度下进行。见特别程序

图示如下。

负电阻测量程序

1 )打开所用主电路中石英晶振单元的两端,并插入可变电阻与晶体单元串联,如图所示。更改电阻值以检查的限制

当时观察到的振荡和电阻(欧姆)。在这种情况下,必须打开电源和关闭,没有失败。

2 )电路中的负电阻(R)是通过上述步骤1 )获得的值和晶体的谐振电阻R1。注意:此测量应在的上限和下限进行工作温度范围。

3 ) C1和C2应在10~30pf范围内使用。如果C1和C2在10pf以下使用或者高于30pf时,有源晶振振荡性能很容易受到影响。驱动器级别可能会增加,或者负电阻可能会降低,因此无法保持振荡。

“推荐阅读”

- Jauch精密振荡器现代定位技术的核心基石

- JauchQuartz新型TCXO产品专为导航应用而生

- Crystek新产品CVCO55CC-1630-1630压控振荡器专用于卫星通信系统

- VTC石英晶体SM5B-20-C-30-30-F-24.000MHz型号参考列表详情

- Fortiming晶振XCS42-20M000-1C25B9频率控制产品系列

- EUROQUARTZ超低电流微型振荡器CXOU3ST-32.768K,50/M

- AEK滤波器A072-164M1型号大全介绍

- Golledge石英晶振GXO-3306G在医疗器械设计中的作用

- ConnorWinfield晶振FTS125系列GPS定时和同步解决方案

- SiTime振荡器SiT1533AI-H4-D14-32.768S老化及其在精密计时中的重要性

相关技术支持

- CTS系列139OCXO以卓越三性能筑牢高频设备核心根基

- KVG石英振荡器T-53S3A2070JXH-LF-26.000MHz数据手册

- Transko石英晶体CS32H-F5050CQ12-65.000M-TR应用说明

- Golledge石英晶振GXO-3306G在医疗器械设计中的作用

- ConnorWinfield晶振FTS125系列GPS定时和同步解决方案

- SiTime振荡器SiT1533AI-H4-D14-32.768S老化及其在精密计时中的重要性

- Statek晶体HGXO3DSTSM320.0M,30/50/I振荡器的操作指南

- 欧洲石英25HDK2261-A-156.250M差分振荡器输出逻辑

- MtronPTI高频XO9095-002R低相位噪声和低g灵敏度OCXO

- Cardinal抖动在高性能设计中的重要性CPPC7L-A5BR-40.0TS

手机版

手机版

添加微信

添加微信