只需了解三件事减少高频抖动给晶振带来的负面影响

只需了解三件事减少高频抖动给晶振带来的负面影响

时钟抖动会对以太网PCI Express和USB3.0等高速协议产生不利影响,时间就是一切,这就是抖动扭曲一切的原因,抖动是系统中预期和实际时序边沿之间的差异,电子元器件石英晶振变得越糟糕-它会对你的系统产生更大的负面影响,抖动与较低的电压阈值成正比,与时钟频率成正比,是高频GHz系统中误码率(BER)的主要来源.

第1点:高性能信号要求接收器具有低抖动

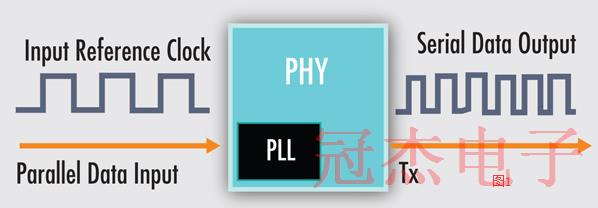

数字系统需要来自石英晶体或晶体振荡器的高精度时钟源,例如,40Gb以太网需要一个抖动小于0.3ps的时钟源,当参考时钟出现抖动时,它会被PHY中的时钟定时器和PLL放大(图1),因为锁相环响应时钟边沿,异相时钟通常会使GHz信号偏离接收端的可接受规格,数据速率越高,源定时源必须越准确.也就是说;随着数据速率的提高,抖动要求会收紧,较低的抖动意味着较低的BER,较低的BER更好.

第2点:从发射器的低抖动时钟源开始

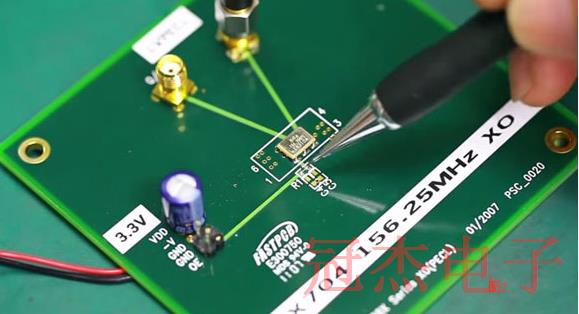

如果HDMI(~10Gbits/s)或USB3.0(5Gbits/s)等GHz信号需要发送器的低抖动,减少时钟晶振抖动的最佳方法是从超"干净"低抖动时钟源开始,虽然抖动在发送端有许多可能的来源,但最大的"降压"可以通过源时钟实现,高质量的时钟源可以扩大系统的抖动容限,减少了石英晶体振荡器扩展和极其复杂的工程工作量的需要,以减少二阶和三阶抖动源,如交叉-PCB中的耦合痕迹或导入的皮肤效应,图2显示了Pericom Semiconductor的晶体振荡器演示板,其具有156.25MHz XO源,该板上安装的XO规格的最大RMS抖动比40Gb以太网所需的最大RMS抖动低0.2ps-30%,在以太网链路上提供了舒适的Rx余量.

要点3:了解如何在系统中使用XO

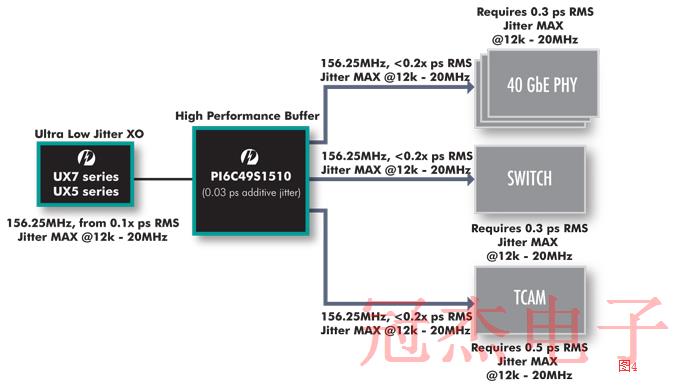

典型的GHz系统如图4所示,超低抖动XO为时钟缓冲器供电,为各种GHz设备提供多个时钟,包括40GbEPHY,以太网交换机和三态内容可寻址存储器(TCAM),第3层路由器的一部分,Pericom的UX7系列XO是低抖动系统的核心,在石英贴片晶振12K-20MHz之间的抖动约为0.1ps(RMS),如图3所示.为了避免在系统中使用多个XO,PI6C49S1510时钟缓冲器可提供多达10个输出时钟(图4中显示了三个),具有0.03ps的极低附加抖动-基本上将XO的低抖动复制到所有输出.

创建低抖动系统的另一种方法是使用图4所示的系统,Pericom的FlexOut时钟发生器,将XO和时钟晶体振荡器缓冲组合到一个封装中,所涉及的频率和对超清晰(低抖动)时钟的需求是FlexOut PI6CXG05F62a具有比前面描述的XO更低的抖动规格的原因(从12K到20的~0.1ps{典型值} /0.15ps{最大值}MHz)并支持LVPECL和LVDS配置中的多达六个输出.

不需要外部XO(这就是重点!),既不需要XO跟踪终端也不需要XO功率滤波器,该振荡器器件采用Pericom专有的晶振定时源,特殊的时钟IC缩小为小型LQFP封装,小于它取代的两个器件.无论设计人员使用哪种架构-XO,XOplus时钟缓冲器,或者像FlexOut-lowBERGHz系统这样的奇特组合设备都需要低抖动,从发射器开始,就在时钟源处.

“推荐阅读”

相关技术支持

- CTS系列139OCXO以卓越三性能筑牢高频设备核心根基

- KVG石英振荡器T-53S3A2070JXH-LF-26.000MHz数据手册

- Transko石英晶体CS32H-F5050CQ12-65.000M-TR应用说明

- Golledge石英晶振GXO-3306G在医疗器械设计中的作用

- ConnorWinfield晶振FTS125系列GPS定时和同步解决方案

- SiTime振荡器SiT1533AI-H4-D14-32.768S老化及其在精密计时中的重要性

- Statek晶体HGXO3DSTSM320.0M,30/50/I振荡器的操作指南

- 欧洲石英25HDK2261-A-156.250M差分振荡器输出逻辑

- MtronPTI高频XO9095-002R低相位噪声和低g灵敏度OCXO

- Cardinal抖动在高性能设计中的重要性CPPC7L-A5BR-40.0TS

手机版

手机版

添加微信

添加微信